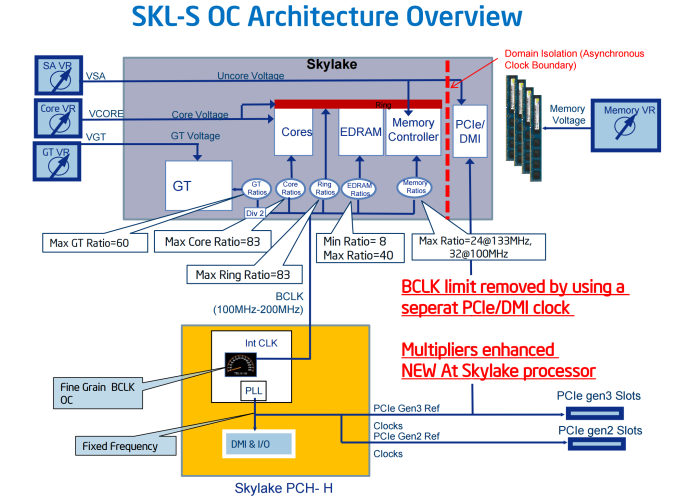

Su skylake slegarono il pci-e dal bclk

https://www.anandtech.com/show/9483/intel-skylake-review-6700k-6600k-ddr4-ddr3-ipc-6th-generation/6

Come dissero in fase di review:

"Previously, when the base frequency was adjusted (100 MHz to 120 MHz), this would push the PCIe frequency too far out of alignment resulting in a lack stability, so the decoupling ratios were there to realign the PCIe clock back to normal (so a ratio of 1.25 means a setting of 120 MHz on the CPU gave 120/125 = 96 MHz on the PCIe, which is more stable). What Skylake does is separate the clock domains altogether, so we get a full range of BCLK adjustments for the processor from 100 MHz to 200-300 MHz in 1 MHz increments. Some motherboard manufacturers have extra components on board to either boost that range to 650 MHz+, or add a finer BCLK adjustment system to allow for 0.0625 MHz steps instead."

Che poi per la cronaca anche le piattaforme più vecchie erano in grado di dividere il bclk dal clock pci-e, ma solo se usati determinati "strap" (ad esempio haswell per tenere il clock pci-e a 100 MHz accettava solo bclk a 100-125-166 MHz)

Sinceramente non so se nelle generazioni successive hanno rimosso questa divisione creata con skylake, ma mi sembrerebbe strano

Per carità, rimane molto più semplice agire di moltiplicatore, perché con il bclk devi stare attento agli altri moltiplicatori e divisori, ma problemi con i device pci-e non dovresti averne sulle piattaforme moderne