Real Black

Utente Èlite

- Messaggi

- 1,290

- Reazioni

- 663

- Punteggio

- 87

A seguito della discussione "Consiglio SSD M2" ho deciso di creare questo thread per fare chiarezza sul brand in questione poiché molto discusso negli ultimi tempi.

Ci tengo a precisare che non sono un ingegnere in questo settore ma soltanto un appassionato e in quanto tale le mie competenze non sono al livello di chi ha studiato il campo per anni, quindi per qualsiasi errore sono disponibile a discuterne nei commenti con eventuali correzioni.

Ci tengo a precisare che non sono un ingegnere in questo settore ma soltanto un appassionato e in quanto tale le mie competenze non sono al livello di chi ha studiato il campo per anni, quindi per qualsiasi errore sono disponibile a discuterne nei commenti con eventuali correzioni.

CHI È YMTC

Yangtze Memory Technology Co. (YMTC) è uno dei principali produttori di NAND flash assieme a Micron, Samsung, SK hynix, Intel/Solidigm (ora parte di Hynix) e Kioxia. Essa nasce nel 2014 a seguito dell’annuncio della Cina di voler intraprendere un percorso R&D (research and development) nel settore delle memorie non volatili, specialmente in quello delle NAND flash, ad oggi la seconda categoria di IC (integrated circuits) più grande.

Dopo il 2014 arriva il 2016, con la fondazione ufficiale sotto tale nome; nel frattempo, l'azienda stessa introduce le sue NAND 32L* MLC (multi-level cell - 2 bit per cella). Dopodiché c’è il 2018, con le NAND 64L TLC (triple-level cell), il 2021 con le 128L TLC e novembre 2022 con le 232L TLC.

Da questa evoluzione ci si può chiedere come ha fatto YMTC ad entrare in un mercato così difficile (perché già nel 2016 ci fu la corsa verso l'impilaggio con più layer possibili) ed essere stato il primo produttore a mettere sul mercato le NAND più alte esistenti, quelle da 232L. Il segreto sta nella sua tecnologia “Xtacking” che andremo ad esaminare.

*: con “L” si intendono i layer, ovvero il numero di word line (WL) o l’”altezza” di una NAND flash. L’aumento dei layer è un’azione che si fa da anni per la diminuzione dei prezzi e per la maggior densità di bit in quanto sono presenti più celle in un array. Ora siamo alle 232L, e i produttori non sembrano voler fermarsi: Samsung prevede di toccare i 1000 layer entro il 2030 (questo intendo con “corsa verso la produzione di NAND con più layer possibili”). Come ancora non si sa, ma questo è un altro discorso.

Fonte: Semiconductor Engineering

Come si può ben vedere, le nostre WL si trovano nel mezzo della NAND flash. Una NAND flash con, per esempio, 232 layer conterrà 232 WL usate per la memorizzazione di dati.

Xtacking

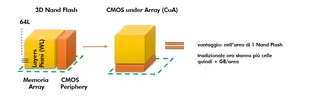

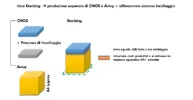

Come già accennato, Xtacking è il fonte di tutta la fama di YMTC. Essa indica la tecnologia per la produzione delle 3D NAND flash. È stata introdotta nel 2018 con il debutto delle 64L. Prima di questo modello - le 32L MLC - YMTC non usava Xtacking ma un’architettura Terabit Cell Array Transistor (TCAT) basata su charge trap flash (CTF), la stessa che attualmente Samsung e Micron usufruiscono.La principale caratteristica di Xtacking è il diverso processo di produzione rispetto agli altri produttori: anziché lavorare l’intera NAND flash su un singolo wafer se ne sfruttano due separati e vengono collegati insieme tramite la tecnica wafer-to-wafer bonding. Sul primo wafer vengono prodotti gli array delle NAND flash (che usano CTF) mentre sul secondo tutta la circuiteria restante: pompe di carica, page buffer, decodificatori delle righe, ecc. Questo insieme di circuiti si chiama “CMOS”. La connessione wafer-to-wafer bonding richiede maggiori procedimenti e maggiori costi rispetto ai metodi di produzione usati da tutti gli altri produttori, non a caso fino a qualche anno fa si dava per spacciata YMTC. Alla fine non è fallita, però TechInsights afferma che non avrà lo stesso passo avuto finora.

Possiamo suddividere Xtacking in tre principali generazioni con ognuna il corrispettivo modello di NAND flash:

- Xtacking 1.0: introduce la tecnologia wafer-to-wafer bonding che verrà usata per le successive generazioni - 64L TLC;

- Xtacking 2.0: viene usato il siliciuro di nichel (NiSi) anziché quello di tungsteno (WSi) per migliorare le performance I/O - 128L TLC/QLC;

- Xtacking 3.0: introduce la tecnica back side source connect (BSSC) abbassando i costi di produzione - 232L TLC.

Fonte: TechInsights

Senza complicarci di troppo la vita, quest'immagine ci riassume i cambiamenti che YMTC ha eseguito da Xtacking 1.0 a Xtacking 3.0. "Double deck" intende dire che le 232 WL sono state suddivise in due insiemi ciascuno avente 116 WL. Questa tecnica è indispensabile per poter impilare più WL possibili.

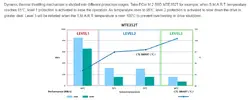

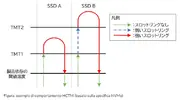

Questi cambiamenti architetturali hanno portato a diversi vantaggi prestazionali, come un aumento dei piani (1 nelle 64L, 2 nelle 128L e 6 nelle 232L), un aumento della velocità per die (le 64L erano da 42 MB/s, le 128L da 70 MB/s e le 232L da presumibilmente più di 150 MB/s) e una diminuzione della tempistica di lettura e programmazione delle celle (rispettivamente tR e tPROG). Va notato anche un aumento della capacità delle memorie avendo drive con capacità sempre più grandi.

WAFER-TO-WAFER BONDING

Non è la prima volta che si sente questo termine; infatti, secondo Wikipedia, questa tecnologia viene usata anche nei sistemi nanoelettromeccanici e microelettromeccanici.Wafer-to-wafer bonding è un tipo di hybrid bonding, ovvero una tecnica per la creazione di legami chimici tra due substrati.

Esistono due tipi di hybrid bonding: quella wafer-to-wafer - utilizzata per le NAND flash e la DRAM - e quella die-to-wafer che è utilizzata principalmente per la HBM (High Bandwidth Memory) DRAM. Parlando della wafer-to-wafer, ci sono più metodi per l’installazione dell’interconnessione tra i due wafer, noi andremo a vedere la cosidetta fusion bonding.

Prendendo come esempio una YMTC 64L, vengono usati due wafer da entrambi 300 mm e, dal momento che uno è dedicato ai transistor CMOS e un altro ai transistor della NAND flash, il primo può operare a temperature più alte senza indurre stress alle celle di memoria. Per la produzione in sé, sono tre i principali step per la corretta implementazione di questa tecnica: processamento del wafer, pre-bonding e la ricottura. È possibile individuare le ragioni per le quali questa tecnologia è costosa e difficile soltanto per i prerequisiti: è necessario avere un wafer che abbia una superficie liscia, piana e pulita e un lavoro fatto alla perfezione, con un'estrema precisione. In caso ci fossero degli errori durante il processamento si avrebbe un dispositivo con malfunzionamenti elettrici causati da delle “bolle” per superficie non connesse.

Soddisfatte queste condizioni, il primo procedimento è la deposizione di legami metallici con la pulizia da ruvidità dei wafer; poi, per facilitare i legami chimici diretti, viene attivata la superficie plasma tramite un gas azoto. Adesso che abbiamo i due wafer pronti possiamo allinearli con precisione in modo tale che si crei una connessione tra di loro e un anche un legame chimico. Come quarto procedimento eseguiamo il processo di ricottura (trattamento termico che altera alcune proprietà chimiche e fisiche dei metalli) per far sì che venga generato un legame di rame, dopodiché le parti di rame si fondono l'uno con l'altro et voilà, i nostri wafer sono pronti per l'uso!

Facile, no? - ovviamente tutta la chimica e la fisica che sta dietro a questa tecnologia non è riassumibile nelle poche righe da me scritte, però per capire a grandi linee il concetto penso che possa andare bene.

RISULTATI

Xtacking 1.0

Qui sopra abbiamo una comparazione tra una NAND YMTC 64L (Xtacking 1.0), una Micron 64L e una NAND 64L che anziché mettere la circuiteria sotto all'array la mette a fianco, nonostante sia un design obsoleto, svantaggioso e in disuso. Si può notare come Xtacking 1.0 porti a dei leggeri vantaggi rispetto ai competitori, tranne nell'efficienza dell'area della NAND, dove c'è una sensibile differenza.

Xtacking 2.0

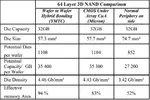

Questa tabella, invece, riporta una comparazione delle specifiche tecniche tra le NAND 128L di YMTC, Samsung, Micron e SK hynix. Qua già si vede un salto un po' più grande, ma, secondo me, confrontando i dati con quelli di SK hynix (riga "Die Size" e "Memory Density"), il gioco non vale la candela.

Xtacking 3.0

Per ultimo c'è Xtacking 3.0, con le 232L. Purtroppo non abbiamo una bella tabella comparativa come quelle di prima, ma conoscendo le specifiche possiamo le NAND flash una per una:

1) YMTC: dimensione del die: 68.15 mm²; densità di bit: 15.03 Gb/mm²;

2) Micron: dimensione del die: 70 mm²; densità di bit: 14.6 Gb/mm²;

3) Samsung: dimensione del die: 89 mm²; densità di bit: 11.5 Gb/mm².

Anche qui YMTC si dimostra essere il vincitore, ma a quanto pare non di troppo.

Ultima modifica:

/cloudfront-us-east-2.images.arcpublishing.com/reuters/XZ7JXIADBNKMFOR3D34AFEUN24.jpg)