adesso che mi ci fai pensare non ricordo, lo lessi su un articolo di PC Professionale, probabilmente confondo le 2 sigle; quello che ricordo è che l'articolo diceva che, al contrario di quanto successo nel passato, il TBW risultava dimezzato rispetto all'analogo modello di generazione precedente, a questo punto devo supporre che fosse il 970 Pro. Della velocità superiore delle celle lo sapevo ma la cosa sulla resistenza mi indispettì non poco perché ho idea che abbaino chiamato 980 Pro qualcosa che avrebbe dovuto chiamarsi 980 EVO ulteriore furbata insomma.

Non solo sugli SSD ma su tutto l'HW è stra-abusato il suffisso PRO, a scopo ingannatorio, perché il PRO dovrebbe richiamare alla mente caratteristiche PROfessionali, quando di professionale non c'è un ciufolo, se non il prezzo in più che bisogna pagare per l'hardware

Sicuramente BAT, si parlava del confronto tra Samsung PRO di generazioni differenti ?.

Le celle MLC del PRO (quelle che hanno scritto mila petabyte nel famoso test) erano proprio il top dell’SSD adatto agli usi assidui di scrittura/professionali. L’unica cosa certa e testata, è proprio che le celle TLC hanno durata inferiore a quelle MLC, “rischiando” poi di vedere un SSD per questi usi, bloccarsi veramente causa usura. TBW definiti da Samsung di conseguenza sono rapportati a questa differenza di celle buone/meno buone.

Si, ha indispettito o meglio deluso anche me e tutti i recensori che scrissero quando uscì il prodotto.

Ora, 2021, è chiaro il motivo di Samsung. La produzione si stava muovendo verso le QLC e figurarsi le celle MLC saranno stati già all’epoca solo a magazzino. Quindi sarebbe mancata la continuità di produzione per il Samsung 980 PRO con celle MLC.

Segno dei tempi! Mentre scrivo, la produzione si è già spostata da 1 anno su celle QLC a 1xx layer con densità impensabili (m.2 consumer con 16 TB on board). I Samsung 990 PRO del 2022 ;)

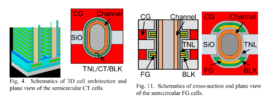

Non tanto per Micron, ora le B37R in su (128L in su, quindi) usano la stessa architettura, quindi replacement gate (RG) su TCAT. Come dici tu è più costosa e porta alcuni svantaggi in termini di densità dei bit (anche se quest'ultimi in questo caso ci sono più per la scelta di Samsung di non usare design multi-stack - più layer "impilati" tra di loro - e COP (Cell Over Periphery)), anche perché non viene lavorato sullo stesso transistor delle memorie a floating gate (FG) e charge trap flash (CTF) (teoricamente), ma d'altro canto assicura un'affidabilità ottima, la migliore, anche per i mezzi di incisione che essa richiede. Ed è per questo che Samsung ha sempre avuto un certo dominio sulle NAND, appunto perché oggettivamente sono le migliori come affidabilità.

Black che pasticcio di termini…

Se dico: Samsung ha perso la leadership delle celle TLC a favore di Micron perché il disegno è superato, non mi puoi rispondere: non è vero per Micron che usano la stessa architettura, sciorinando poi un elenco di termini da manuale delle nand fuori dal contesto, chiudendo che le celle Samsung sono le migliori come affidabilità.

Cosa centra l’affidabilità se parlo di costi o prestazioni?

Cosa rende più affidabile per te una cella Samsung rispetto ad una di un competitor?

Le celle del Samsung 970 PRO dai petabyte non sono più quelle; studi che dimostrano l’affidabilità di una cella su un'altra non ce ne sono (anche perché troppo recenti di produzione). Io non ho neanche sentito di marche di SSD le cui celle sono buggate e per questo i prodotti ritirati dal mercato.

Quindi mi sembra proprio solo una tua idea. Le celle sono buone tutte. La “bontà” è un discorso da fare solo confrontando; MLC vs TLC vs QLC.

Facciamo un po di chiarezza sui termini che hai scritto.

Floating gate (FG) non le fanno più da un po’, dai tempi, per Micron, della partnership con Intel 64 layer (tecnologia ormai superata da tutti) ma sembra che Micron ne abbia ancora in magazzino e sono servite ancora per le sue 128 layer.

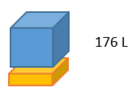

Replacement gate (RG), come citi all’inizio, è per le NAND 176 layer Micron, non per le 128 layer.

Tutti hanno celle Charge Trap (CTF).

La differenza è nella struttura da cui dal silicio si ricava la cella e i materiali usati per creare il tunnel e gate in cui vengono intrappolati gli elettroni del semiconduttore. Differisce dalla tecnologia a gate flottante convenzionale in quanto utilizza un film di nitruro di silicio per immagazzinare elettroni anziché il silicio policristallino. Una cosa un po più efficiente e meno costosa. stop. [cit. Wikipedia]

Invece per quanto riguarda il discorso di economia che ho accennato prima rispetto alle celle Samsung:

Le celle Micron 128 layer sono proprio quelle confrontabili con le V6 (sedici die da 512 Gb per i modelli di SSD più capienti) di Samsung.

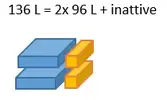

I pacchetti NAND Samsung V6 sono composti da 2 stack - (stack - trattasi del pacchetto base della NAND 3D, naturalmente visto quanto scritto sopra, è costituito da 32 die da 512 GB) - perché nascono da una tecnologia più vecchia (quella che faceva detenere a Samsung il primato di densità delle TLC sui competitor).

In parole povere prendi 2 chip 9x layer, li sovrapponi, per crearne uno di dimensione (densità) di 1xx layer (spiegazione sintetica).

Le NAND BICs Toshiba, SK Hynix e Micron nuove (ognuno con le proprie caratteristiche, che se vuoi possiamo approfondire, ma che alcune sono simili/uguali) sono progettate diversamente da quelle Samsung (essendo venute dopo e avendo conosciuto il know out di Samsung). Sono a litografia minore e gli stack possono arrivare a densità molto maggiori (cioè ogni pacchetto può contenere nell’unità di area più memoria -> GB).

Ne discendono due cose. La prima è che per ogni chip prodotto dai competitor di Samsung il costo del materiale è maggiore, MA (due), essendo i chip dei competitor di Samsung più densi (cioè ogni pacchetto porta più TB), ne servono meno su un SSD per raggiugere quel tot di TB e quindi l’SSD costerà meno. Il risultato è/sarà per SSD >2TB che Samsung deve riprogettare a breve le proprie NAND per stare sul mercato.

E questo è un fatto.

Poi se vuoi parliamo delle differenze tecniche che citi: COP vs altre.

Facciamo un disegnino che magari è più esplicativo a beneficio di chi legge e si vorrebbe interessare dell’argomento.

La V6 Samsung è una vertical-channel 3D charge trap (CTF). Anzi è stata la prima a produrre in massa questo tipo di 3D NAND.

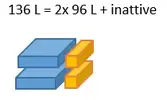

Come detto è realizzata da 2 stack sovrapposti (hanno disponibile la produzione base TLC 96 layer…la usano).

Il disegno dello stack (lascio fuori i termini tecnici ulteriori), hanno word-line e control gate in una parte laterale all’incisione delle die. Ok, non sono stato di parola: la cella FGMOSFET è realizzata per stampo dal silicio o die, con 2 circuiti a bassissima tensione che permettono di scrivere/leggere/cancellare la cella stessa…un apparato di controllo in comunicazione poi con il controller (semplifico, non me ne vogliano gli esperti dell’argomento).

Nelle celle Samsung questo apparato è realizzato tecnicamente a fianco dello stampo, quindi si vedrà una cosa del genere: in blu la porzione di stack con le celle in arancione l’apparato di controllo.

Ora, competitor Samsung, che hanno avuto modo di lavorare meglio negli ultimi anni (SK hynix e Micron), pur iniziando col presentare un design a quattro piani, che raddoppiano il parallelismo, (ma aggiungendo appunto ogni volta quel al circuito periferico, che a sua volta occupa prezioso spazio sul die), hanno inventato un disegno diverso, per rendere più dense e modulari gli stack.

Si tratta della tecnologia CMOS Under Array (CUA) o Periphery Under Cell (PUC).

Come detto Micron a differenza di Samsung e SKh utilizza ancora

per questa generazione di NAND, il Floating gate (FG).

Le celle CTF però tendono ad essere più piccole rispetto alle celle a gate flottante e il design complessivo offre una migliore capacità di ridimensionamento all'aumentare del numero di strati.

Perché Micron usa ancora una tecnologia obsoleta? Perché ne ha prodotta molto in passato e deve smaltirla.

Vediamo quindi la differenza tra il chip Samsung e quello dei competitor.

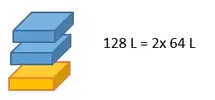

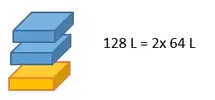

SK hynix pubblicizza la propria memoria come TLC 128 L 4D, Micron rimane sul “tradizionale” TLC 3D.

Vado a prendere le parole di Sean Webster della redazione di Tom’s Hardware USA

“Tradizionalmente, la logica dei circuiti periferici si trova ai margini dell'array di celle NAND, occupando potenzialmente fino al 40% dello spazio del die e limitando così la scalabilità. Spostando la logica sotto l'array, i produttori possono ottenere progetti di livello superiore mantenendo un'elevata efficienza dell'array. Il concetto di posizionare i circuiti periferici sotto le celle di memoria (PuC) non è nuovo. Di fatto, questa tecnologia è attualmente implementata su flash NAND di Intel e Micron sotto forma di tecnologia CMOS under Array (CuA).”

Quindi abbiamo lo spostamento dell’apparato di controllo sotto e ne viene:

1) la produzione più economica del singolo stack

2) la programmazione è più semplice e veloce (e meno energivora)

3) gli stack essendo più sottili possono essere in numero maggiore (più piani = più memoria per unità di superficie)

Si può aggiungere che le celle a 128 L di SK hynix sono “migliori” di quelle a 128 L di Micron, poiché queste di tipo FG sono più grandi… quindi meno dense, meno veloci, più energivore, e… più costose.

Giusto come dicevi nel tuo intervento Black, ma contestualizzato qui con le celle di pari livello SKH e non quelle Samsung che in sintesi: costano di più produrle perché ce ne vanno di più per ottenere i GB o TB dei competitor. Ma il discorso è più ampio perché investe anche lo spreco, infatti:

128 L = 2x 64 L è meglio di 136 L = 2x 96 L + inattive

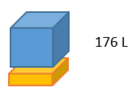

Il futuro… per esempio per Micron con la NAND 176 layer è stato ottenuto rivedendo completamente la struttura di un FGMOSFET (cella 3D). Niente più separazione tra le singole celle: il gate di controllo le avvolge, risparmiando corrente e dialogando con le celle molto più velocemente.

Quindi la differenza non è come prima nella disposizione dell’apparato di controllo, ma proprio in come viene stampata la die; si introduce un gate di "sostituzione" (RG), che utilizza linee metalliche altamente conduttive invece di uno strato di silicio

Mi devo avvalere di un disegno già fatto

“Il gate di controllo stesso, invece di essere in polisilicio è in metallo, il che riduce la resistenza elettrica e consente l’utilizzo di algoritmi di lettura e scrittura semplificati, che consentono alla 3D NAND da 176 strati di scrivere, leggere e cancellare fino a due volte più velocemente di un’attuale 3D NAND.

La nuova architettura permette inoltre di ottenere una dimensione dello stampo inferiore di circa il 30% rispetto alle migliori offerte del settore.”.

Si tratta del chip di memoria più denso realizzato, ovvero M.2 vendibili a prezzi di produzione più bassi e a capienza più alti… ovazione per Micron!

Insomma, motivo in più per Samsung per aggiornarsi e riempire il gap, invece di dormire sui (meritati) allori di questi ultimi 3 anni.

Facendo il disegnino anche di questi chip di memoria avremo questo.

La preoccupazione di Samsung era di poter mantenere una produzione di alta qualità e ottenere buoni rendimenti senza il rischio di disallineamenti dei fori dei canali dello stack.

In questa nuova tipologia di chip lo stack può raggiungere da solo le densità precedenti senza eventuali problemi tecnici.

Ecco quindi una panoramica pseudo-tecnica delle tecnologie attuali delle NAND e di quelle che si affacciano sul panorama commerciale del prossimo futuro.

L'I/O delle 128L è da 1.2 Gb/s, non 1.4/1.6 Gb/s. Quello della settima generazione (17xL) è invece da 2.0 Gb/s. Che poi è un po' una cosa che lascia desiderare visto che ci sono NAND con lo stesso I/O (per esempio le Samsung 32, 48 e 64L sono tutte da 1 Gb/s) ma con velocità in MB/s per die ben diverse, infatti viene più usata questo come mezzo per definire la velocità per die di una NAND che il suo I/O espresso in Gb/s o MT/s (o MTps). Per esempio, le 128L di Samsung da 512Gb hanno una velocità di 82 MB/s, mentre le 128L di Kioxia (BiCS5) sempre da 512Gb sono da 132 MB/s, infatti più veloci, anche se hanno un I/O più lento (1066 MT/s, ma alla fine è una cosa che dipende anche dalla velocità dei canali del controller sull'SSD finale).

Io leggo sul datasheet che le 96L – 128L raggiungono una velocità di interfaccia di 1200 MTps, mentre i 176L possono ora raggiungere velocità di 1.600 MTps tramite l'interfaccia ONFI (per Micron. Idem Kioxia che dalle recensioni (anche di Tom’s Hardware) cita in proposito.

https://www.tomshardware.com/news/micron-now-shipping-176-layer-3d-tlc-nand-flash

La Samsung V6 è una 136L (96L ca 650 MTps x2)

Con MTps si intende la velocità dell’interfaccia a processare operazioni, e non GBps.