- Messaggi

- 12,289

- Reazioni

- 6,324

- Punteggio

- 208

Ora, i dispositivi 3D NAND 2yyL sono disponibili. Aziende leader del settore 3D NAND come Samsung, SK hynix/Solidigm, Micron, KIOXIA/Western Digital e YMTC continuano a correre verso il futuro delle applicazioni di storage ad alta velocità e alta densità. Le tecnologie 3D NAND avanzate, tra cui array di celle multi-stacking, legame ibrido con array NAND e chip logici CMOS, e le soluzioni di package, sono descritte nella roadmap.

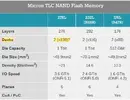

Samsung ha recentemente introdotto la V-NAND V9 con 286 strati attivi. La prossima V-NAND V10 adotterà la tecnologia di legame ibrido come i prodotti KIOXIA 218L BiCS8 CBA e YMTC Xtacking. Micron ha anche recentemente rilasciato 276L con una struttura a 3 deck. KIOXIA/WD BiCS9 verrà saltato e passerà direttamente alla BiCS10 con 332L.

La prima memoria flash si è evoluta in due dimensioni (scalatura laterale). Con l'avanzare della tecnologia di scalatura lineare e spaziale degli array di celle di memoria, la capacità di memoria e la densità di memoria per die di silicio sono gradualmente migliorate. La scalatura è diventata una fonte di competizione tra i produttori di memorie flash, ma il limite è stato raggiunto quando gli array di celle di memoria, linea e spazio, hanno raggiunto il processo a 15 nm. Ciò è dovuto a un numero crescente di problemi che non potevano più essere ignorati, tra cui il fatto che le celle di memoria si avvicinano troppo tra loro, causando dispersione di corrente, o che il numero di elettroni immagazzinati in una cella di memoria diminuisce, compromettendo l'affidabilità delle prestazioni di lettura/scrittura.

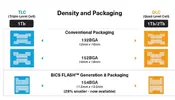

Il passo successivo nell'evoluzione della memoria flash è consistito nell'impilamento delle celle di memoria in tre dimensioni (scalatura verticale). L'aumento del numero di strati comporta un aumento del numero di celle di memoria per unità di superficie, con conseguente maggiore capacità e integrazione. Nel 2007, KIOXIA ha annunciato la tecnologia di memoria flash 3D per l'impilamento delle celle di memoria. Nel 2015, KIOXIA ha commercializzato una memoria flash 3D a 48 strati con il marchio BiCS FLASH.*1Da allora, KIOXIA ha rilasciato prodotti BiCS FLASH circa ogni due anni, con un numero crescente di livelli. Nel 2021, KIOXIA ha rilasciato la sesta generazione di BiCS FLASH, composta da 162 livelli.

Questa discussione riguarda le BiCS 8 (8ª generazione di 3D NAND di KIOXIA/WD), che per un certo verso rappresentano una svolta nelle tecnologia delle moderne nand flash, nel miglioramento delle prestazioni e della densità di memoria, applicando le due nuove tecnologie, CBA (CMOS direttamente legato all'array) e OPS (On Pitch SGD).

Alla conferenza ISSCC di febbraio 2025, Kioxia e Sandisk hanno fornito maggiori dettagli sul chip flash NAND BiCS8 che le aziende distribuiranno a breve.

La memoria FLASH BiCS di ottava generazione ha 218 livelli, ed una velocità operativa di (3200 MT/s.

"Questo significa circa il 5% di livelli in meno rispetto ai prodotti concorrenti della stessa generazione (ad esempio, le memorie flash 3D con circa 230 livelli).

Il numero di 218 strati dei BIC appare leggermente deludente rispetto ai 238 strati di SK Hynix , ai 238 strati della NAND di Samsung, alla tecnologia a 232 strati di Micron e ai 232 strati Xtacking di YMT, nonostante l'alto contenuto tecnologico intrinseco.

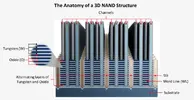

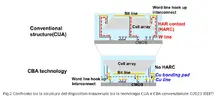

BiCS, come tutte le nand flash 3D, è costituito da due componenti: l'array di celle di memoria in cui vengono memorizzati i dati (in azzurro e verde) e i circuiti CMOS che controllano l'array di celle di memoria (in grigio).

Nel nodo tecnologico precedente (le precedenti BiCS), i circuiti CMOS e l'array di celle di memoria venivano fabbricati su un singolo wafer, con tutte le limitazioni che questo comporta (n. di layer, gestione array, gestione dell'intero pacchetto).

L'elevato numero di strati sembra aver reso la logica così complessa che un approccio CUA (CMOS Under Array) standard avrebbe dovuto dedicare un'area molto ampia alla logica, e l'array di bit di memoria vero e proprio non avrebbe dovuto essere così grande.

Per risolvere anche questo problema, Kioxia ha sviluppato la tecnologia CBA (CMOS directly Bonded to Array), in cui i due wafer vengono lavorati separatamente per i circuiti CMOS e l'array di celle di memoria, per poi essere saldati o in gergo "incollati":

A sinistra, la precedente CUA (CMOS Under Array, cioè i transistor posizionati sotto l'array di celle) in cui appunto il substrato di materiale di Silicio (Si SUB) viene lavorato aggiungendo i transistor di controllo (CMOS) e a questo, costruito sopra l'array di celle 3D.

A destra il nuovo metodo CBA, con la doppia lavorazione di CMOS da una parte e array di celle dall'altra, per poi essere incollati uno sull'altro in posizione capovolta.

Questo nuovo metodo di creazione delle Nand Flash consente di utilizzare una maggiore temperatura per la realizzazione della parte "array", cosa non possibile precedentemente per via della porzione CMOS più sensibile. Inoltre con questo metodo si riesce a ridurre sensibilmente i disturbi elettrici tra le celle di memoria adiacenti sempre nella creazione dell'array.

Per il futuro inoltre, grazie alla tecnologia CBA avanzata, sarà possibile realizzare memorie flash 3D multi-stacked con due o più CMOS e due o più array di celle.

L'"hybrid bonding" (la tecnica di incollaggio), introdotta nel settore delle Nand Flash grazie alle 3D Xtacking di YMTC, si è affermato come un fattore abilitante fondamentale per il packaging dei semiconduttori di nuova generazione.

BiCS8 differirà significativamente dai suoi predecessori poiché utilizzerà un approccio di bonding ibrido per arrivare a realizzare celle 3D da 332 strati (2 x 218L).

Un altra novità di queste BiCS 8 è OPS (On-Pitch SGD) un sistema di struttura della Die che consente una maggiore densità di celle nei loro chip a 218 strati perché riducono le dimensioni delle celle sia lateralmente che verticalmente. Questo, a loro dire, produce una maggiore capacità in un die più piccolo con meno strati, a un costo ottimizzato.

Per spiegare cosa avviene con l'adozione del OPS, facciamo un passo indietro e spieghiamo come è fatta una cella 3D tipo:

Figura 1

Figura 1 Figura 2

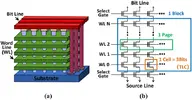

Figura 2Il modello di DIE 3D (figura 2), cioè ciò che esce dal produttore di celle e che viene confezionato assemblandone "un tot" in un pacchetto tipo questo BGA (figura 1) che è quello che troviamo sul pcb dell'ssd insieme al Controller, delle eventuali DRAM e a vari circuiti, è in se realizzato da diverse componenti.

Come si può vedere, la base è un "wafer" realizzato con un alternanza di materiali (vedi pacchetto azzurro/grigio Source Plate); l'impilamento di un elettrodo a piastra che funge da gate di controllo (le piastre azzurre) e di un isolante (grigio) .

Al materiale (per le BiCS 8 è composto da almeno 218 piani di materiale non isolante) vengono praticati dei fori microscopici che vengono rivestiti - con tecniche avveniristiche - di materiali alternati (semiconduttore/isolante).

In questa condizione, l'intersezione tra l'elettrodo a piastra e l'elettrodo a colonna costituisce una cella di memoria:

Figura 3

Figura 3Come funziona la programmazione di ogni cella?

Vedete figura 3, ho cerchiato nell'esempio 3 celle create all'intersezione di 3 diversi piani di materiale non isolante ed il rispettivo foro.

Word Line (WL)

Fila di gate condiviso orizzontalmente che seleziona la cella all’interno della stringa per le operazioni di programmazione (scrittura), lettura e cancellazione.

Bit Line (BL)

Fila verticale che collega la sorgente/drenaggio di ciascuna cella al circuito di sensing, usato per applicare tensioni di programmazione/lettura e per misurare la corrente durante la lettura.

Select Gate (SG)

Transistor di selezione posto all’inizio (SGS) e/o alla fine (SGD) di ogni stringa di celle, che abilita o isola l’intera stringa dal bit line o dalla source line a seconda dell’operazione.

Source Line (SL)

Linea comune di massa (o sorgente) condivisa da tutte le stringhe del blocco; serve per completare il percorso di corrente durante programmazione ed erase.

Tutte queste linee che collegano una singola cella (o gruppo di esse), ortogonali e parallele tra loro, permettono di:

- Programmare o scrivere

- Leggere il valore

- Cancellare

In definitiva si tratta di un meccanismo simile al vecchio gioco della "battaglia navale", ricordate?

Due coordinate arrivano ad una ed una sola cella e, se ogni linea porta tensioni diverse, può avvenire la magia.

Come si vede in Figura 2.

Programmazione (Scrittura)

Si alza la tensione sulla word line (WL) (tensione più grande) per favorire l’iniezione di elettroni nel floating gate.

La bit line (BL) e la source line (SL) restano a tensione bassa (piccola tensione).

Il select gate d’ingresso è acceso (tensione più grande) per collegare la stringa alla BL, mentre quello d’uscita è spento (piccola tensione) per isolare la sorgente.

Lettura

Si applica una piccola tensione alla WL e alla BL per verificare se la cella conduce.

Entrambi i select gate sono accesi (tensione più grande) per connettere la cella alla BL e alla SL.

La corrente misurata sulla BL indica lo stato logico del floating gate.

Cancellazione

La WL e la BL vengono portate a tensione bassa (piccola tensione).

I select gate sono spenti (piccola tensione) per isolare completamente la stringa.

Sulla source line (SL) si applica una tensione più grande, ma di polarità inversa, per rimuovere gli elettroni dal floating gate.

In tutti i casi, il corretto bilanciamento tra piccole tensioni (6–8 V) e tensioni più grandi (15–20 V) sui vari segnali garantisce il funzionamento affidabile della cella 3D NAND.

Facendo riferimento a Figura 2, il wafer quando viene "bucherellato", perde di consistenza ed è a rischio deformazione. Per rendere più rigida la struttura del DIE, ogni qualche mm di questo wafer è fatto attraversare da dei tagli di irrigidimento (li vedete in grigio in verticale), fatti ovviamente da un materiale isolante che non interferisce con le celle.

Queste tracce di materiale di irrigidimento tagliano anche dei fori, dunque le celle in corrispondenza di queste vengono perse costituendo vere e proprie "stringhe di memoria fittizie" (VC).

On-Pitch SGD (OPS) di Toshiba/Sandisk su BiCS 8, opera proprio sincronizzando la posizione dei fori con la posizione dei tagli di irrigidimento del DIE.

Osservando in un DIE convenzionale, la configurazione del select-gate e delle stringhe di memoria nel piano, l'isolante che separa il select-gate (la fessura dell'isolante) si sovrappone alle stringhe di memoria fittizie che non funzionano come celle di memoria nel nodo tecnologico precedente.

D'altra parte, nell'OPS, la fessura dell'isolante è posizionata tra le stringhe di memoria elettricamente attive e le stringhe di memoria fittizie vengono eliminate per aumentare la densità di memoria.

OPS, stando alle dichiarazioni del produttore, ha migliorato la scalabilità laterale, eliminando il più possibile le stringhe di memoria fittizie (invece di 24 righe di VC attivo/fittizio, vengono utilizzate solo 20 righe di VC attivo), con un conseguente impacchettamento sull'asse y (direzione BL) del 16,7%. La densità di bit aumenta di oltre il 50 percento, risultando nella più alta densità di bit tra le memorie NAND 3D TLC a 2XX strati.

-------

Spero vi abbia interessato e di avere usato un linguaggio meno tecnico possibile, ma se avete dubbi o volete chiarimenti, siamo quì.

Ultima modifica: