- Messaggi

- 27,911

- Reazioni

- 13,605

- Punteggio

- 254

Per chi fosse interessato all'elettronica digitale, qui trova i primi cenni alla stessa.

http://www.ge.infn.it/~fontanel/dispense.pdf

http://www.ge.infn.it/~fontanel/dispense.pdf

Segui il video qui sotto per vedere come installare il nostro sito come web app sulla tua schermata principale.

Nota: Questa funzionalità potrebbe non essere disponibile in alcuni browser.

Pubblicità

:DL'elettronica, assieme all'informatica, alla matematica e alla fisica mi hanno sempre affascinato...

Tuttavia non so nulla (almeno per le altre cose qualcosina so), e per me quel testo è troppo complicato, fin troppo arabo! :lol:

Qualcosa di più semplice per un deficiente come me? Grazie mille!

P.S. Egregio signor Blume(rs :P ) sono rimasto affascinato dai suoi post e dalle sue discussioni! Mi faccia suo discepolo aprendomi le porte della Sacra Conoscenza dell'Elettronica! :inchino:

Ho già intenzione di comprare breadboard (tral'altro ho trovato una 400 fori a 2 euro) e relativi cavetti, ma non so come orientarmi per il resto (Arduino? Raspy?).

L'elettronica, assieme all'informatica, alla matematica e alla fisica mi hanno sempre affascinato...

Tuttavia non so nulla (almeno per le altre cose qualcosina so), e per me quel testo è troppo complicato, fin troppo arabo! :lol:

Qualcosa di più semplice per un deficiente come me? Grazie mille!

P.S. Egregio signor Blume(rs :P ) sono rimasto affascinato dai suoi post e dalle sue discussioni! Mi faccia suo discepolo aprendomi le porte della Sacra Conoscenza dell'Elettronica! :inchino:

Ho già intenzione di comprare breadboard (tral'altro ho trovato una 400 fori a 2 euro) e relativi cavetti, ma non so come orientarmi per il resto (Arduino? Raspy?).

Io leggo sempre con piacere l'amico gronag, una fonte, da dove poter sempre attingere...:ok:La dispensa linkata da @Blume è incompleta ma illustra la materia in modo chiaro e semplice :sisi:

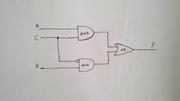

Di solito nell'elettronica digitale (sarebbe meglio chiamarla "Cibernetica", come la studiai io più di 30 anni fa) si parte dalle studio di base dei sistemi di numerazione (binario, ottale, esadecimale, ecc.), dei codici (BCD, Gray, ASCII, ecc.) e dell'algebra booleana, per poi passare all'analisi delle reti combinatorie e sequenziali, fino a giungere ad affrontare le tecniche di progettazione delle memorie, dei convertitori DAC (digitali-analogici) e ADC (analogico-digitali) e dei microprocessori :sisilui:

Per quanto riguarda, in particolare, lo studio delle famiglie logiche, bipolari e unipolari, è necessario avere le conoscenze di base dell'elettronica dei dispositivi bipolari e unipolari (BJT, JFET e MOSFET):

http://www.dieet.unipa.it/mosca/Elettronica/Capitolo 13.pdf :sisilui:

A presto :ciaociao:

P.S. Leggi anche i miei articoli a partire dal post #4 :D