- Messaggi

- 12,264

- Reazioni

- 6,301

- Punteggio

- 208

Propongo un approfondimento a chi fosse interessato al funzionamento (teorico) del modo in cui vengono memorizzate le informazioni in un SSD (generico).

Questo video di Micron ci dà l'idea del processo che dalla progettazione porta alla produzione di dispositivi di memorizzazione SSD.

Ho preso come esempio il transistor di tipo SLC planare con tecnologia a gate flottante.

Questa è la cella più semplice cui sono nel tempo seguite varie evoluzioni. Il principio di funzionamento però rimane sostanzialmente lo stesso.

Di seguito gli elementi costituenti una cella tipo:

La base di qualsiasi cella di questo tipo è il SEMICONDUTTORE. Il silicio è isolante, ma, drogato ad esempio con fosforo, che ha un elettrone in più, diventa conduttore, con una concentrazione di elettroni pari alla concentrazione di atomi di fosforo. Infatti l'elettrone in più * risulta poco legato e con poca energia diventa libero, ossia passa nella banda di conduzione, mentre gli altri elettroni partecipano al legame atomico.

Il fenomeno viene detto: OSSIDAZIONE.

La memorizzazione nella cella Nand Flash avviene grazie a questi elettroni liberi, per mezzo di una carica elettrica bassa che viene fatta passare nel semiconduttore e che genera ossidazione, con passaggio di elettroni ad un apposito materiale la cui carica (negativa) persiste al cessare della corrente elettrica che l'ha generata.

Sono 3 i fenomeni fisici che avvengono in una cella nand:

La corrente elettrica, (da Source a Drain) che fatta passare, provoca l'eccitazione degli elettroni che non partecipano al legame atomico *.

L'ossidazione di un materiale (substrato) capace di rilasciare elettroni a bassissima carica elettrica (semiconduttore).

Infine l'effetto tunnel (o tunneling)un fenomeno della fisica quantistica che si osserva in determinate condizioni per cui una particella carica (elettrone, fotone), essendo particella con una massa ma anche onda, è capace di attraversare una sostanza solida; in questo caso gli elettroni sono capaci di attraversare con poca energia una barriera isolante (floating gate). Gli elettroni rimangono intrappolati in questo strato isolante al cessare della corrente elettrica che ha determinato lo spostamento degli elettroni.

Ecco il principio che spiega la ritenzione del bit nella cella, anche quando l'SSD non è alimentato.

Il dato memorizzato nella cella non è altro che la presenza o no di questi elettroni intrappolati tra gli strati isolanti.

Per fare in modo che da ogni cella si rilevi un valore (bit) e che nell'insieme costituiscano dei dati memorizzati, le celle vengono organizzate strutturalmente in un array, gruppi, che condividono linee a cui sono applicate tensioni elettriche e organizzate in modo logico come i dispositivi già presenti sul mercato (HDD).

Vediamo di seguito nello specifico la struttura del chip di memoria di un SSD (sempre la semplice cella SLC planare) in un ipotetico teardown.

Sull'SSD identifichiamo, oltre al Controller e alla memoria DRAM, i chip di memoria.

Questi sono costituiti da un rivestimento serigrafato attorno ad uno o più stampi (DIE).

Il DIE è l'unità più piccola che può eseguire indipendentemente comandi.

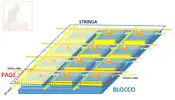

All'interno una DIE è formata da array di celle a uno o due piani interconnessi. I piani (2 nell'esempio sopra) hanno permesso di far stare più celle sull'unità di superficie, un'idea presto messa in pratica nella creazione delle celle 3D. I piani sono importanti per la struttura della cella ma non hanno una funzione specifica nella memorizzazione dei dati.

Invece si può dire che ogni DIE è organizzato a livello logico da un definito numero di BLOCCHI, che costituiscono l'unità di memorizzazione più piccola di un certo dato memorizzato (4K o 512 byte).

Il BLOCCO è un insieme di celle isolate elettricamente ma la struttura logica di memorizzazione suddivide ogni blocco in N. PAGINE.

Una pagina costituisce l'array di celle più piccolo in cui esse sono organizzate. Per le celle prese in esame ogni blocco contiene tipicamente pagine da 32 o 64 byte.

Ogni pagina organizza le celle che la costituiscono suddividendo le linee elettriche controllate dal Controller del dispositivo.

Vediamo di seguito come è organizzato un BLOCCO e come funziona la memorizzazione (programmazione), la lettura e infine la cancellazione di un dato, a livello di un vero e proprio circuito elettrico.

Questo è lo schema semplificato delle connessioni di un BLOCCO di celle NAND Flash:

Di per se ogni cella non avrebbe molto valore, ma la combinazione di molte celle è ciò che consente l'archiviazione d quantità significative di dati. Il primo passo per combinare singole celle NAND è la STRINGA (stiamo guardando dentro il singolo blocco):

Una stringa (vedi figura sotto) è l'insieme delle celle collegate alla medesima Bit-line e collegate in un punto alla Source-line (collega le sorgenti "S" delle singole stringhe). A sua volta ogni singola celle della stringa è collegata alla Word-line (ortogonalmente quindi).

Ciò vuol dire che ogni stringa contiene due meccanismi di controllo in serie con le altre celle NAND. Un meccanismo serve per programmare e cancellare, mentre un altro consente di leggere la cella.

Una stinga di celle NAND può memorizzare 32 bit di dati, questo si traduce comunque solo in 4 byte di dati o sufficienti per 4 caratteri. Le stringhe (mostrate come colonne nello schema sotto) sono l'unità minima da leggere e sono in genere composte da 32 o 64 celle.

Ma come si riesce ad inviare gli input di programmazione, erase o leggere il dato sulla stringa?

I transistor String Select e Ground Select sono collegati alla String Select Line (SSL) e alla Ground Select Line (GSL). Questi elementi di controllo sono a loro volta collegati attraverso delle linee al canale di comunicazione del Controller.

La stringa rappresenta il verso di programmazione e (teoricamente) cancellazione delle celle NAND.

Dato perà che l'elemento fondamentale della memorizzazione è la lettura, tutte le celle che condividono la stessa Word-line sono l'unità minima da programmare ed anche il senso in cui vengono lette le celle della stringa.

Queste sono le PAGINE e vengono rappresentate (si veda la figura sopra) ortogonalmente alle stringhe. Così come la stringa rappresenta il verso di programmazione, la pagina ne rappresenta quello di lettura.

In genere una pagina è costituita da almeno qualche decina di migliaia di celle NAND, e con molti dei più recenti dispositivi raggiungono dimensioni per pagina di 128K se non 256K e 512K. La maggior parte delle dimensioni di una pagina si indicano come 2K, 4K, 8K, ecc (dimensione sempre in byte).

L'insieme delle pagine costituisce un blocco.

Un blocco è una matrice bidimensionale composta da pagine (righe) e stringhe (colonne). Il numero totale di bit in un blocco può essere calcolato moltiplicando il numero di stringhe per il numero di pagine.

Per capire il meccanismo delle tre operazioni delle celle (programmazione/cancellazione/lettura), ho pensato di farvi vedere una ipotetica vista tridimensionale dell'array:

Si immagina sempre un blocco ideale realizzato con poche celle NAND Flash, cui ho assegnato alcune lettere identificative.

Breve riassunto di cosa si è visto prima:

Scrivere una cella vuol dire far passare una leggera corrente elettrica tra Drain (verde) e Source (giallo), cioè mettere in contatto Source-line e Bit-line, in modo che il semiconduttore (in blu), rilasci una specifica quantità di elettroni che vengono, per effetto tunneling, intrappolati nel floating gate.

Cancellare una cella vuol dire applicare una carica di tensione più elevata (sempre tra Drain e Source) che interrompe il tunneling e restituisce al semiconduttore la carica accumulata nel floating gate.

Quando invece si vuole leggere se una particolare cella ha il valore "0" piuttosto di "1", occorre far passare un determinato voltaggio (rappresenta la soglia di carica di quegli elettroni intrappolati), attraverso il Control gate (in arancione): se la corrente elettrica tra Source e Control gate passa senza variazioni di tensione, vuol dire che non ci sono elettroni nel floating gate, per cui il valore è "1".

Se la corrente elettrica è ostacolata dalla carica negativa degli elettroni intrappolati, la cella avrà un valore "0".

Succedono però altre cose.

Al comando dell'host della scrittura, il controller esegue una ricerca e identifica i blocchi vuoti (cancellati).

Quindi inizia la scrittura riempiendo sequenzialmente le pagine del blocco e andando al blocco libero successivo.

Per scrivere ad esempio la cella "A" la base della cella viene fatta oggetto del passaggio di una lieve corrente elettrica, specifica (ne troppo forte ne troppo debole, ma studiata per liberare gli elettroni del substrato). Gli elettroni si depositano sulla porta in prossimità del Control gate.

Naturalmente se il primo valore della pagina sulla cella "A" fosse "1" la cella non viene programmata, lasciando il valore già presente (cella cancellata=1).

Durante l'operazione di cancellazione è necessaria una grande tensione negativa per respingere gli elettroni dal Floating gate, ciò si ottiene collegando a terra il Control gate e applicando 20V al substrato, attraverso le Bit-line e Source-lines (Matrice IP-Well). Di conseguenza, gli elettroni vengono rimossi dal Floating gate a causa dell'effetto tunneling già visto.

Si dice che "un SSD può programmare ogni singola cella ma quando cancella, può solo cancellare l'intero blocco", vero ma... vediamo perchè.

Quando l'host ha un file da scrivere l'SSD inizia a scrivere una pagina alla volta. Per farlo utilizza, come detto, la Source-line e la Bit-line a bassa tensione sul substrato, attivate nel momento per ottenere su ogni cella un valore 1/0.

Dovendo cancellare la singola cella per riscriverci nuovi dati, occorre svuotare/cancellare la relativa pagina cui appartiene la cella.

Ad esempio se devo scrivere inizio con 1 BIT su “A”, poi su “B”, ECC

L'operazione di cancellazione applica sulla Souce line una alta tensione che rende cancellata (valore 1), TUTTA la relativa pagina.

Quindi ora abbiamo un blocco costituito da pagine cancellate e pagine ancora valide… teoricamente la cosa (programmazione parziale delle pagine) DOVREBBE FUNZIONARE; Sebbene abbiamo ritardato l'esecuzione delle operazioni di cancellazione spostando in modo intelligente i dati su pagine diverse, a un certo punto chiaramente non rimarranno pagine vuote e le cancellazioni diventeranno essenziali. È qui che arrivano le cattive notizie: per eseguire una cancellazione ci vuole molte volte più tempo che per eseguire una lettura o una programmazione . E questo ha chiaramente delle conseguenze sulle prestazioni se non gestito correttamente.

Oltre al rallentamento dell'SSD c'è un secondo fattore più importante che ha reso la programmazione parziale delle pagine una soluzione non adottata concretamente: la tensione più alta di cancellazione investendo tutto il substrato del blocco (che è unico), crea un DISTURBO che può cambiare lo stato delle celle attigue.

La soluzione ad entrambe i problemi è stata quella di considerare i blocchi isole autonome (lo sono elettricamente).

Un'operazione di cancellazione su un chip flash cancella i dati da tutte le pagine nel blocco , quindi se alcune delle altre pagine contengono dati attivi (dati da conservare) occorre prima copiarli altrove.

Ecco perché una pagina può essere modificata (cioè scritta) solo dopo che l'intero blocco a cui appartiene è stato cancellato

La conseguenza più immediata (come già accennato) è che è necessario preparare nuovi blocchi vuoti (cancellati) prima della programmazione (cioè, cancellare prima della scrittura).

Inoltre, l'operazione di cancellazione ha una latenza molto più lunga rispetto alle operazioni di lettura e programmazione.

Spero l'argomento vi abbia interessato e se avete domande sull'argomento, forza!